在Vivado中使用FIFO IP核时,valid信号(通常称为rd_valid或dout_valid)是一个重要的控制信号。让我详细解释它的作用和使用场景。

valid信号的作用:

-

功能:

- valid信号是一个输出信号,用于指示FIFO输出数据的有效性。

- 当FIFO成功读出一个数据项并将其呈现在输出端口时,valid信号会被置高。

-

时序:

- 通常,valid信号与输出数据同步,或比输出数据晚一个时钟周期。

- 它与rd_en(读使能)信号相关,但可能有不同的时序关系,取决于FIFO的具体配置。

-

用途:

- 提供数据有效性的指示。

- 帮助接收端正确识别和处理有效数据。

- 在某些设计中,用于同步或控制数据流。

什么时候应该勾选valid:

-

异步读取操作:

- 当FIFO的读取操作不是每个时钟周期都进行时。

- 在读时钟和写时钟不同的异步FIFO设计中。

-

复杂的数据流控制:

- 当下游逻辑需要精确知道何时有有效数据可用时。

- 在实现数据流水线或数据处理链时。

-

突发读取操作:

- 当FIFO被配置为支持突发读取模式时。

- 在这种情况下,valid信号可以指示每个突发周期中的有效数据。

-

低功耗设计:

- 在需要最小化数据处理功耗的设计中,valid信号可以用来控制下游逻辑的使能。

-

数据完整性验证:

- 当需要确保没有遗漏任何数据项时。

- 在要求高可靠性的系统中,用于验证数据传输的完整性。

-

调试和监控:

- 在系统调试阶段,valid信号可以提供额外的可见性,帮助识别数据流问题。

示例场景:

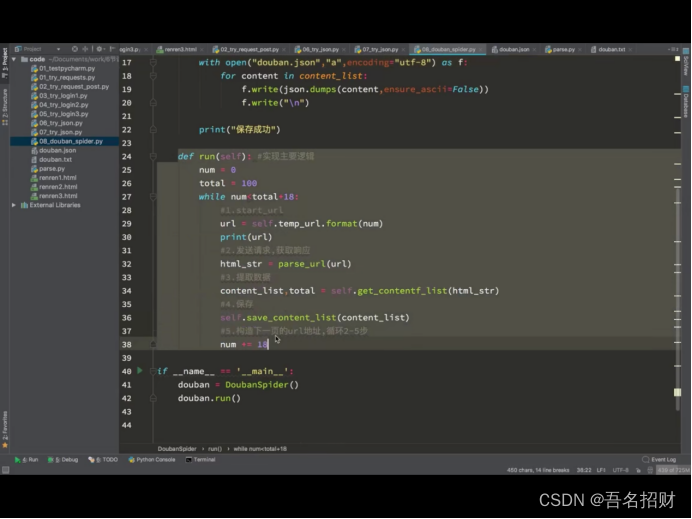

假设一个数据处理系统,其中FIFO用于缓冲来自异步源的数据。以下是一个简单的Verilog代码示例,展示了如何使用valid信号:

module data_processor (

input wire clk,

input wire rst,

input wire [7:0] fifo_data,

input wire fifo_valid,

output reg rd_en,

output reg [7:0] processed_data,

output reg data_ready

);

reg [1:0] state;

localparam IDLE = 2'b00, READ = 2'b01, PROCESS = 2'b10;

always @(posedge clk or posedge rst) begin

if (rst) begin

state <= IDLE;

rd_en <= 1'b0;

processed_data <= 8'd0;

data_ready <= 1'b0;

end else begin

case (state)

IDLE: begin

rd_en <= 1'b1; // 请求读取数据

state <= READ;

data_ready <= 1'b0;

end

READ: begin

rd_en <= 1'b0;

if (fifo_valid) begin

// 有效数据可用,开始处理

state <= PROCESS;

end

end

PROCESS: begin

processed_data <= fifo_data + 8'd1; // 简单的数据处理

data_ready <= 1'b1;

state <= IDLE;

end

endcase

end

end

endmodule

在这个例子中,处理器模块使用fifo_valid信号来确定何时有有效数据可用于处理。这确保了只有在有效数据到达时才进行处理,从而提高了系统的效率和可靠性。

总结:

选择是否使用valid信号主要取决于您的具体应用需求。如果设计涉及异步操作、需要精确的数据流控制,或者在调试过程中需要更多的可见性,那么启用valid信号是一个很好的选择。对于简单的同步设计,如果可以确保每个读取操作都会产生有效数据,那么可以不使用此信号,以简化设计。